# University syllabus

### Module-1

**Diode Circuits:** Review of diodes as rectifiers (No question shall be set from review portion). Diode clipping and clamping circuits.

**Transistor biasing and stabilization**: Operating point, analysis and design of fixed bias circuit, self-bias circuit, Emitter stabilized bias circuit, voltage divider bias circuit, stability factor of different biasing circuits. Problems.

**Transistor switching circuits:** Transistor switching circuits, PNP transistors, thermal compensation techniques.

### Module-2

**Transistor at low frequencies:** BJT transistor modelling, CE fixed bias configuration, voltage divider bias, emitter follower, CB configuration, collector feedback configuration, analysis using h – parameter model, relation between h – parameters model of CE, CC and CB modes, Millers theorem and its dual.

**Transistor frequency response:** General frequency considerations, low frequency response, Miller effect capacitance, high frequency response, multistage frequency effects.

### Module-3

**Multistage amplifiers:** Cascade and cascode connections, Darlington circuits, analysis and design. **Feedback amplifiers:** Feedback concept, different types, practical feedback circuits, analysis and design of feedback circuits.

### Module-4

**Power amplifiers**: Amplifier types, analysis and design of different power amplifiers, distortion in power amplifiers.

**Oscillators:** Principle of operation, analysis and derivation of frequency of oscillation of phase shift oscillator, Wien bridge oscillator, RF and crystal oscillator and frequency stability.

### Module-5

**FETs:** Construction, working and characteristics of JFET and MOSFET. Biasing of JFET and MOSFET, JFET and MOSFET amplifiers, analysis and design.

| Table of | Contents |

|----------|----------|

|----------|----------|

| Sl.No | Modules                                            | Page no. |

|-------|----------------------------------------------------|----------|

| 1     | Diode circuits and transistor biasing              | 03       |

| 2     | Transistor at low frequency and frequency response | 53       |

| 3     | Multistage amplifier and feedback amplifier        | 77       |

| 4     | Power amplifier and oscillator                     | 98       |

| 5     | FETs                                               | 146      |

# Module-1

# **Diode circuits**

### **Diode:**

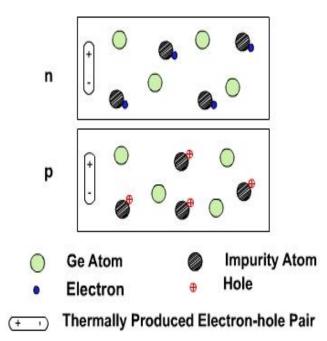

A pure silicon crystal or germanium crystal is known as an intrinsic semiconductor. There are not enough free electrons and holes in an intrinsic semi-conductor to produce a usable current. The electrical action of these can be modified by doping means adding impurity atoms to a crystal to increase either the number of free holes or no of free electrons.

When a crystal has been doped, it is called a extrinsic semi-conductor. They are of two types

- n-type semiconductor having free electrons as majority carriers

- p-type semiconductor having free holes as majority carriers

- By themselves, these doped materials are of little use. However, if a junction is made by joining ptype semiconductor to n-type semiconductor a useful device is produced known as diode. It will allow current to flow through it only in one direction. The unidirectional properties of a diode allow current flow when forward biased and disallow current flow when reversed biased. This is called rectification process and therefore it is also called rectifier.

- How is it possible that by properly joining two semiconductors each of which, by itself, will freely conduct the current in any direct refuses to allow conduction in one direction.

- Consider first the condition of p-type and n-type germanium just prior to joining <u>fig. 1</u>. The majority and minority carriers are in constant motion.

- The minority carriers are thermally produced and they exist only for short time after which they recombine and neutralize each other. In the mean time, other minority carriers have been produced and this process goes on and on.

- The number of these electron hole pair that exist at any one time depends upon the temperature. The number of majority carriers is however, fixed depending on the number of impurity atoms available. While the electrons and holes are in motion but the atoms are fixed in place and do not move.

- Holes from the p-side diffuse into n-side where they recombine with free electrons.

- Free electrons from n-side diffuse into p-side where they recombine with free holes.

- The diffusion of electrons and holes is due to the fact that large no of electrons are concentrated in one area and large no of holes are concentrated in another area.

- When these electrons and holes begin to diffuse across the junction then they collide each other and negative charge in the electrons cancels the positive charge of the hole and both will lose their charges.

- The diffusion of holes and electrons is an electric current referred to as a recombination current. The recombination process decay exponentially with both time and distance from the junction. Thus most of the recombination occurs just after the junction is made and very near to junction.

- A measure of the rate of recombination is the lifetime defined as the time required for the density of carriers to decrease to 37% to the original concentration

- The impurity atoms are fixed in their individual places. The atoms itself is a part of the crystal and so cannot move. When the electrons and hole meet, their individual charge is cancelled and this leaves the originating impurity atoms with a net charge, the atom that produced the electron now lack an electronic and so becomes charged positively, whereas the atoms that produced the hole now lacks a positive charge and becomes negative.

- The electrically charged atoms are called ions since they are no longer neutral. These ions produce an electric field as shown in **fig. 3**. After several collisions occur, the electric field is great enough to repel rest of the majority carriers away of the junction. For example, an electron trying to diffuse from n to p side is repelled by the negative charge of the p-side. Thus diffusion process does not continue indefinitely but continues as long as the field is developed.

- This region is produced immediately surrounding the junction that has no majority carriers. The majority carriers have been repelled away from the junction and junction is depleted from

• The physical width of the depletion region depends on the doping level. If very heavy doping is used, the depletion region is physically thin because diffusion charge need not travel far across the junction before recombination takes place (short life time). If doping is light, then depletion is more wide (long life time).

The symbol of diode is shown in **fig. 4**. The terminal connected to p-layer is called anode (A) and the terminal connected to n-layer is called cathode (K)

#### Fig.4

#### **Reverse Bias:**

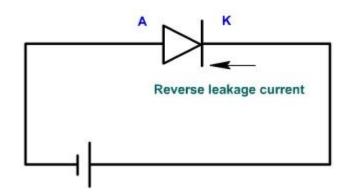

If positive terminal of dc source is connected to cathode and negative terminal is connected to anode, the diode is called reverse biased as shown in <u>fig. 5</u>.

#### Space charge capacitance C<sub>T</sub> of diode:

Reverse bias causes majority carriers to move away from the junction, thereby creating

more ions. Hence the thickness of depletion region increases. This region behaves as the dielectric material used for making capacitors. The p-type and n-type conducting on each side of dielectric act as the plate. The incremental capacitance  $C_T$  is defined by

$$C_{T} = \left| \frac{dQ}{dV} \right|$$

$\mathbf{5}$

15EE34

Since  $i = \frac{dQ}{dt}$

Therefore,  $i = C_T \frac{dV}{dt}$  (E-1)

- where, dQ is the increase in charge caused by a change dV in voltage.  $C_T$  is not constant, it depends upon applied voltage, there fore it is defined as dQ / dV.

- When p-n junction is forward biased, then also a capacitance is defined called *diffusion* capacitance  $C_D$  (rate of change of injected charge with voltage) to take into account the time delay in moving the charges across the junction by the diffusion process. It is considered as a fictitious element that allow us to predict time delay.

- If the amount of charge to be moved across the junction is increased, the time delay is greater, it follows that diffusion capacitance varies directly with the magnitude of forward current.

$$C_{\rm D} = \frac{dQ}{dV} = \frac{I\tau}{dV} \qquad (E-2)$$

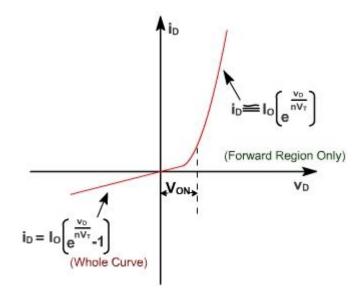

#### **Relationship between Diode Current and Diode Voltage**

An exponential relationship exists between the carrier density and applied potential of diode junction as given in equation E-3. This exponential relationship of the current  $i_D$  and the voltage  $v_D$  holds over a range of at least seven orders of magnitudes of current - that is a factor of  $10^7$ .

$$i_{D} = I_{D} \left[ \exp\left(\frac{qV_{D}}{nkT}\right) - 1 \right] = I_{D} \left[ e^{\left(\frac{qV_{D}}{nkT}\right)} - 1 \right]$$

(E-3)

Where,

$i_D$ = Current through the diode (dependent variable in this expression)  $v_D$ = Potential difference across the diode terminals (independent variable in this expression)  $I_O$ = Reverse saturation current (of the order of 10<sup>-15</sup> A for small signal diodes, but  $I_O$  is a

strong function of temperature)

$q = Electron charge: 1.60 \times 10^{-19} joules/volt$

- k = Boltzmann's constant:  $1.38 \times 10^{-23}$  joules /° K

- T = Absolute temperature in degrees Kelvin ( $^{\circ}$ K = 273 + temperature in  $^{\circ}$ C)

n = Empirical scaling constant between 0.5 and 2, sometimes referred to as the Exponential Ideality Factor

For germanium diodes, n is usually considered to be close to 1. For silicon diodes, n is in the range of 1.3 to 1.6. n is assumed 1 for all junctions all throughout unless otherwise noted.

Equation (E-3) can be simplified by defining  $V_T = k T/q$ , yielding

$$i_{D} = I_{O} \left[ e x p \left( \frac{v_{D}}{n V_{T}} \right) - 1 \right] = I_{O} \left[ e^{\left( \frac{v_{D}}{n V_{T}} \right)} - 1 \right]$$

(E-4)

At room temperature (25°C) with forward-bias voltage only the first term in the parentheses is dominant and the current is approximately given by

$$\dot{b} = l_0 e^{\frac{V_0}{\eta V_T}}$$

(E-5)

The current-voltage (I-V) characteristic of the diode, as defined by (E-3) is illustrated in <u>fig. 1</u>. The curve in the figure consists of two exponential curves. However, the exponent values are such that for voltages and currents experienced in practical circuits, the curve sections are close to being straight lines. For voltages less than  $V_{ON}$ , the curve is approximated by a straight line of slope close to zero. Since the slope is the conductance (i.e., i / v), the conductance is very small in this region, and the equivalent resistance is very high. For voltages above  $V_{ON}$ , the curve is approximated by a straight line with a very large slope. The conductance is therefore very large, and the diode has a very small equivalent resistance.

15EE34

### Fig.1 - Diode Voltage relationship

The slope of the curves of **fig.1** changes as the current and voltage change since the l-V characteristic follows the exponential relationship of relationship of equation (E-4). Differentiate the equation (E-4) to find the slope at any arbitrary value of v<sub>D</sub>or i<sub>D</sub>,

$$\frac{di_{D}}{dv_{D}} = \frac{l_{O}}{nV_{T}} \exp\left(\frac{v_{D}}{nV_{T}}\right) = \frac{l_{O}}{nV_{T}} e^{\frac{v_{D}}{nV_{T}}}$$

(E-6)

This slope is the equivalent conductance of the diode at the specified values of  $v_D$  or  $i_D$ .

We can approximate the slope as a linear function of the diode current. To eliminate the exponential function, we substitute equation (E-4) into the exponential of equation (E-7) to obtain

$$\exp\left(\frac{v_{D}}{n \vee_{T}}\right) = \frac{i_{D}}{i_{0}} + 1 = \left(\frac{di_{D}}{dv_{D}}\right) \left(\frac{n \vee_{T}}{i_{0}}\right)$$

(E-7)

A realistic assumption is that  $I_0 << i_D$  equation (E-7) then yields,

$$\frac{\mathrm{d}\mathbf{i}_{\mathrm{D}}}{\mathrm{d}\mathbf{v}_{\mathrm{D}}} = \frac{\mathbf{i}_{\mathrm{D}} + \mathbf{I}_{\mathrm{O}}}{\mathrm{n}\,\mathbf{V}_{\mathrm{T}}} \approx \frac{\mathbf{i}_{\mathrm{D}}}{\mathrm{n}\,\mathbf{V}_{\mathrm{T}}}$$

(E-8)

The approximation applies if the diode is forward biased. The dynamic resistance is the reciprocal of this expression.

$$r_{d} = \frac{n V_{T}}{i_{D} + i_{O}} \approx \frac{n V_{T}}{i_{D}}$$

(E-9)

- Although  $r_d$  is a function of  $i_d$ , we can approximate it as a constant if the variation of  $i_D$  is small. This corresponds to approximating the exponential function as a straight line within a specific operating range.

- Normally, the term  $R_f$  to denote diode forward resistance.  $R_f$  is composed of  $r_d$  and the contact resistance. The contact resistance is a relatively small resistance composed of the resistance of the actual connection to the diode and the resistance of the semiconductor prior to the junction. The reverse-bias resistance is extremely large and is often approximated as infinity.

### **Temperature Effects:**

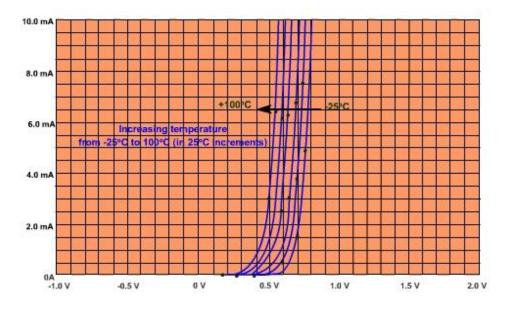

Temperature plays an important role in determining the characteristic of diodes. As temperature increases, the turn-on voltage, v<sub>ON</sub>, decreases. Alternatively, a decrease in temperature results in an increase in v<sub>ON</sub>. This is illustrated in <u>fig. 2</u>, where V<sub>ON</sub> varies linearly with temperature which is evidenced by the evenly spaced curves for increasing temperature in 25 °C increments.

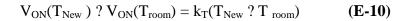

The temperature relationship is described by equation

where,

$T_{room}$  = room temperature, or 25°C.

$T_{New}$  = new temperature of diode in °C.

$V_{ON}(T_{room})$  = diode voltage at room temperature.

$V_{ON}$  ( $T_{New}$ ) = diode voltage at new temperature.

$k_T$  = temperature coefficient in V/°C.

Although  $k_T$  varies with changing operating parameters, standard engineering practice permits approximation as a constant. Values of  $k_T$  for the various types of diodes at room temperature are given as follows:

$k_T$ = -2.5 mV/°C for germanium diodes  $k_T$  = -2.0 mV/°C for silicon diodes

The reverse saturation current,  $I_O$  also depends on temperature. At room temperature, it increases approximately 16% per °C for silicon and 10% per °C for germanium diodes. In other words,  $I_O$ approximately doubles for every 5 °C increase in temperature for silicon, and for every 7 °C for germanium. The expression for the reverse saturation current as a function of temperature can be approximated as

$$I_{0}(atT_{2}) = I_{0}(atT_{1})exp(k_{i}(T_{2} - T_{1})) = I_{0}(atT_{1})e^{K_{i}(T_{2} - T_{1})}$$

(E-11)

where  $K_i = 0.15/^{\circ}C$  (for silicon) and T1 and T2 are two arbitrary temperatures.

#### **Diode Operating Point**

#### Example - 1:

When a silicon diode is conducting at a temperature of 25°C, a 0.7 V drop exists across its terminals. What is the voltage,  $V_{ON}$ , across the diode at 100°C?

#### Solution:

The temperature relationship is described by

$V_{ON}(T_{New})$  ?  $V_{ON}(T_{room}) = K_T (T_{New}$  ?  $T_{room})$

or,  $V_{ON}(T_{New}) = V_{ON}(T_{room}) + K_T(T_{new}?T_{room})$

Given  $V_{ON} (T_{room}) = 0.7 \text{ V}, T_{room} = 25^{\circ} \text{ C}, T_{New} = 100^{\circ} \text{ C}$

Therefore,  $V_{ON} (T_{New}) = 0.7 + (-2 \times 10^{-3}) (100-75) = 0.55 \text{ V}$

#### Example - 2:

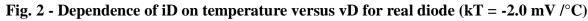

Find the output current for the circuit shown in <u>fig.1(a)</u>.

### Fig.1- Circuit for Example 2

#### Solutions:

- Since the problem contains only a dc source, we use the diode equivalent circuit, as shown in <u>fig.</u> <u>1(b)</u>. Once we determine the state of the ideal diode in this model (i.e., either open circuit or short circuit), the problem becomes one of simple dc circuit analysis.

- It is reasonable to assume that the diode is forward biased. This is true since the only external source is 10 V, which clearly exceeds the turn-on voltage of the diode, even taking the voltage division into account. The equivalent circuit then becomes that of **fig. 1(b)**. with the diode replaced by a short circuit.

The Thevenin's equivalent of the circuit between A and B is given by fig. 1(c).

The output voltage is given by

1215EE34

$$v_{o} = \left(\frac{5 - V_{ON}}{3 + R_{f}}\right) (2 + R_{f}) + V_{ON}$$

or

$$v_{o} = \frac{10 + V_{ON} + 5R_{f}}{3 + R_{f}}$$

or,

If  $V_{ON} = 0.7V$ , and  $R_f = 0.2 W$ , then

$$V_{o} = 3.66V$$

### **Diode Operating Point**

#### Example - 3

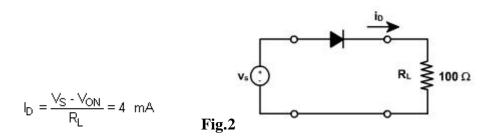

The circuit of <u>fig. 2</u>, has a source voltage of Vs = 1.1 + 0.1 sin 1000t. Find the current, iD. Assume that

nVT = 40 mV

VON = 0.7 V

#### Solution:

We use KVL for dc equation to yield

$V_s = V_{ON} + I_D R_L$

This sets the dc operating point of the diode. We need to determine the dynamic resistance so we can establish the resistance of the forward-biased junction for the ac signal.

$$r_{\rm D} = \frac{n \, \bigvee_{\rm T}}{\rm I_{\rm D}} = 10 \, \, \Omega$$

Assuming that the contact resistance is negligible Rf= rD Now we can replace the forwardbiased diode with a 10 W resistor. Again using KVL, we have,

vs= Rf id + RL id

$$i_{d} = \frac{v_{S}}{R_{f} + R_{L}} = 0.91 \sin 1000 t \text{ mA}$$

The diode current is given by

I = 4 + 0.91 sin 1000 t mA

Since iD is always positive, the diode is always forward-biased, and the solution is complete.

This sets the dc operating point of the diode. We need to determine the dynamic resistance so we can establish the resistance of the forward-biased junction for the ac signal.

$$r_D = \frac{n V_T}{I_D} = 10 \Omega$$

Assuming that the contact resistance is negligible Rf= rD Now we can replace the forwardbiased diode with a 10 W resistor. Again using KVL, we have,

The diode current is given by

I = 4 + 0.91 sin 1000 t mA

Since iD is always positive, the diode is always forward-biased, and the solution is complete.

**Diode Operating Point**

**Small Signal Operation of Real diode:**

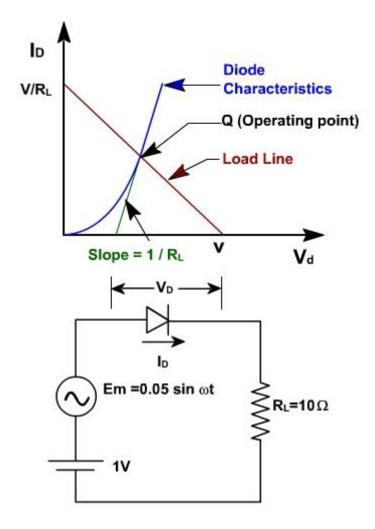

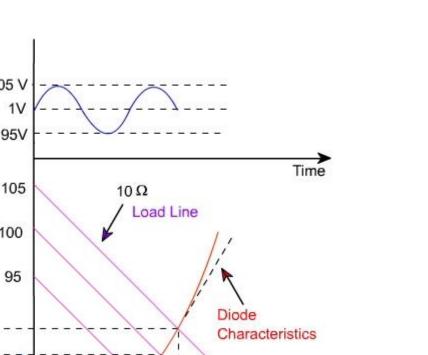

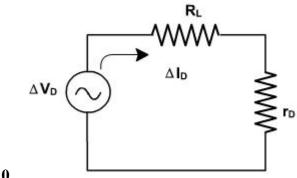

Consider the diode circuit shown in **fig. 3**.

$V = V_D + I_d R_L$  $V_D = V - I_d R_L$

This equation involves two unknowns and cannot be solved. The straight line represented by the above equation is known as the **load line**. The load line passes through two points,

15EE34

and

$I = 0, V_D = V$  $V_D = 0, I = V / R_L.$

The slope of this line is equal to 1/ RL. The other equation in terms of these two variables VD & Id, is given by the static characteristic. The point of intersection of straight line and diode characteristic gives the operating point as shown in <u>fig. 4</u>.

ohm.

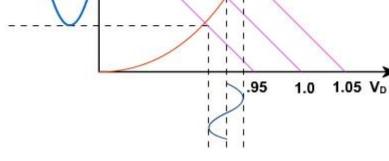

The resulting input voltage is the sum of dc voltage and sinusoidal ac voltage. Therefore, as the diode voltage varies, diode current also varies, sinusoidally. The intersection of load line and diode characteristic for different input voltages gives the output voltage as shown in <u>fig. 6</u>.

15EE34<sup>14</sup>

Total 1.05 V voltage

Applied

Ь in m 11

.95V

100

95

Fig. 6

In certain applications only ac equivalent circuit is required. Since only ac response of the circuit is considered DC Source is not shown in the equivalent circuit of fig. 7. The resistance rf represents the dynamic resistance or ac resistance of the diode. It is obtained by taking the ratio of  $\Delta$  VD/  $\Delta$  ID at operating point.

Dynamic Resistance  $\Delta$  rD =  $\Delta$  VD /  $\Delta$  ID

Let us consider a circuit shown in fig. 5 having dc voltage and sinusoidal ac voltage. Say

$$V = 1V, RL = 10$$

**Fig. 7**

### **Applications of Diode**

**Diode Approximation: (Large signal operations):**

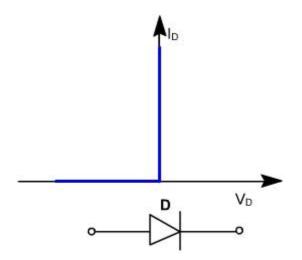

#### 1. Ideal Diode:

- When diode is forward biased, resistance offered is zero,

- When it is reverse biased resistance offered is infinity. It acts as a perfect switch.

The characteristic and the equivalent circuit of the diode is shown in fig. 1.

Fig. 1

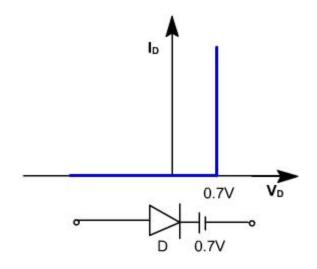

- 2. Second Approximation:

- When forward voltage is more than 0.7 V, for Si diode then it conducts and offers zero resistance. The drop across the diode is 0.7V.

- When reverse biased it offers infinite resistance.

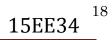

15EE34<sup>17</sup>

The characteristic and the equivalent circuit is shown in fig. 2.

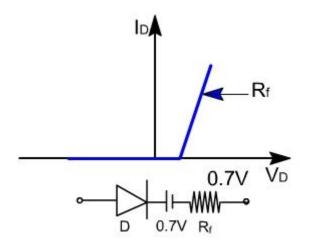

- 3. 3rd Approximation:

- When forward voltage is more than 0.7 V, then the diode conducts and the voltage drop across the diode becomes 0.7 V and it offers resistance Rf (slope of the current)

**VD**= **0.7** + **ID Rf**.

The output characteristic and the equivalent circuit is shown in fig. 3.

• When reverse biased resistance offered is very high & not infinity, then the diode equivalent circuit is as shown in <u>fig. 4</u>.

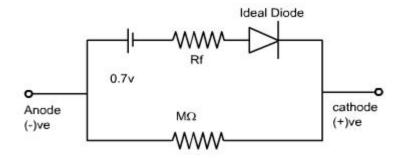

### Example - 1:

Calculate the voltage output of the circuit shown in fig. 5 for following inputs

- (a)  $V_1 = V_2 = 0$ .

- (b)  $V_1 = V, V_2 = 0.$

- (c) V<sub>1</sub> = V<sub>2</sub> = V knew voltage =  $V_r$

Forward resistance of each diode is R<sub>f</sub>.

### Solution:

(a). When both  $V_1$  and  $V_2$  are zero , then the diodes are unbiased. Therefore,

$V_o = 0 V$

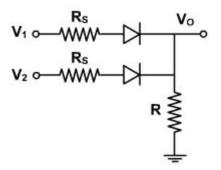

(b). When  $V_1 = V$  and  $V_2 = 0$ , then one upper diode is forward biased and lower diode is unbiased. The resultant circuit using third approximation of diode will be as shown in <u>fig. 6</u>.

Applying KVL, we get

- $V=I(R_{f}+R_{s}+R)+V_{r}$  $\therefore I=\frac{V-Vr}{R_{s}-R_{f}+R}$

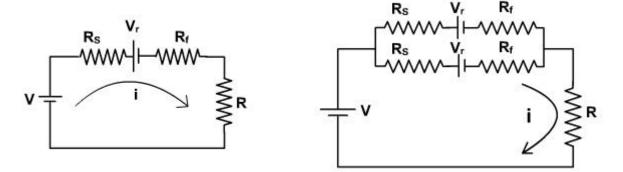

- (c) When both  $V_1$  and  $V_2$  are same as V, then both the diodes are forward biased and conduct. The resultant circuit using third approximation of diode will be as shown in **Fig. 7**.

$$V = \frac{1}{2} (R_{f} + R_{s}) + V_{r} + 1$$

$$I = \frac{V - V_{r}}{\left(\frac{R_{s} + R_{f}}{2} + R\right)}$$

#### Half wave Rectifier:

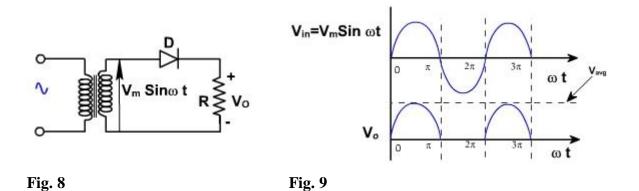

The single ? phase half wave rectifier is shown in fig. 8.

In positive half cycle, D is forward biased and conducts. Thus the output voltage is same as the input voltage. In the negative half cycle, D is reverse biased, and therefore output voltage is zero. The output voltage waveform is shown in **fig. 9**.

The average output voltage of the rectifier is given by

$$\bigvee_{avg} = \frac{1}{2} \int_{0}^{\pi} \bigvee_{m} \sin \omega t \, d(\omega t)$$

$$= \frac{\bigvee_{m}}{\pi} = 0.318 \bigvee_{m}$$

The average output current is given by

$$I_{avg} = \frac{V_m}{\pi R}$$

When the diode is reverse biased, entire transformer voltage appears across the diode. The maximum voltage across the diode is  $V_m$ . The diode must be capable to withstand this voltage. Therefore PIV half wave rating of diode should be equal to  $V_m$  in case of single-phase rectifiers. The average current rating must be greater than  $I_{avg}$

#### **Full Wave Rectifier:**

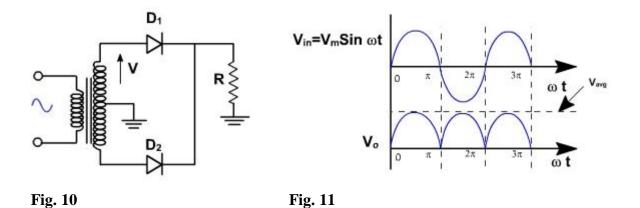

A single ? phase full wave rectifier using center tap transformer is shown in <u>fig. 10</u>. It supplies current in both half cycles of the input voltage.

In the first half cycle  $D_1$  is forward biased and conducts. But  $D_2$  is reverse biased and does not conduct. In the second half cycle  $D_2$  is forward biased, and conducts and  $D_1$  is reverse biased. It is also called 2 ? pulse midpoint converter because it supplies current in both the half cycles. The output voltage waveform is shown in **fig. 11**.

The average output voltage is given by

15EE34

$$\bigvee_{avg} = \frac{1}{\pi_0} \int_{0}^{\pi} \bigvee_{m} \sin \omega t \, d(\omega t)$$

$$= \frac{2 \bigvee_{m}}{\pi}$$

and the average load current is given by

$$l_{avg} = \frac{2 Vm}{\pi R}$$

When  $D_1$  conducts, then full secondary voltage appears across  $D_2$ , therefore PIV rating of the diode should be 2  $V_m$ .

### **Bridge Rectifier:**

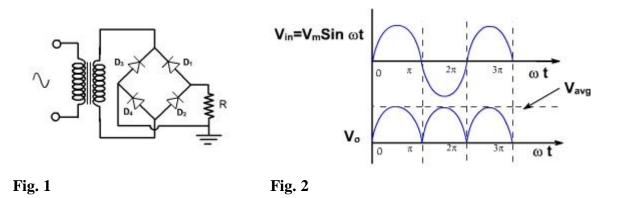

The single ? phase full wave bridge rectifier is shown in <u>fig. 1</u>. It is the most widely used rectifier. It also provides currents in both the half cycle of input supply.

- In the positive half cycle,  $D_1 \& D_4$  are forward biased and  $D_2 \& D_3$  are reverse biased. In the negative half cycle,  $D_2 \& D_3$  are forward biased, and  $D_1 \& D_4$  are reverse biased. The output voltage waveform is shown in <u>fig. 2</u> and it is same as full wave rectifier but the advantage is that PIV rating of diodes are V m and only single secondary transformer is required.

- The main disadvantage is that it requires four diodes. When low dc voltage is required then secondary voltage is low and diodes drop (1.4V) becomes significant. For low dc output, 2-pulse center tap rectifier is used because only one diode drop is there.

The ripple factor is the measure of the purity of dc output of a rectifier and is defined as

Ripple factor =

$$\frac{r.m.s \text{ value of the acoutput voltage}}{average dc output voltage}$$

$$= \sqrt{\sqrt{2}^{2} + \sum_{n=1}^{\infty} \sqrt{2}^{n}}$$

Therefore,

Ripple factor =

$$\frac{\sqrt{\bigvee_{ms}^2 - \bigvee_0^2}}{\bigvee_0}$$

=  $\sqrt{\left(\frac{\bigvee_{ms}}{\bigvee_0}\right)^2 - 1}$

### **Clippers:**

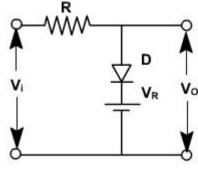

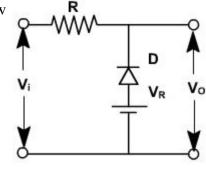

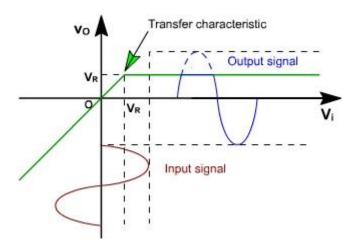

Clipping circuits are used to select that portion of the input wave which lies above or below some reference level. Some of the clipper circuits are discussed here. The transfer characteristic ( $v_o$  vs  $v_i$ ) and the output voltage waveform for a given input voltage are also discussed.

### **Clipper Circuit 1:**

In this clipper circuit,

If  $v_i < V_R,$  diode is reversed biased and does not conduct. Therefore,  $v_o = v_i$

and,  $\text{ if } v_i > V_R \text{, diode is forward biased and thus, } v_o = V_R \text{.}$

The transfer characteristic of the clippers is shown in <u>fig. 4</u>. Fig. 3

#### Fig. 4

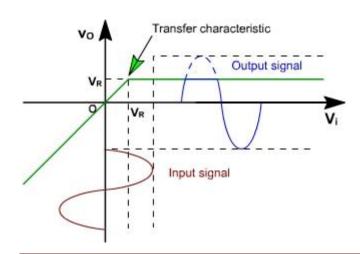

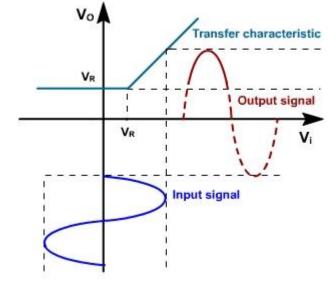

### **Clipper Circuit 2:**

The clipper circuit shown in <u>fig. 5</u> clips the input signal below reference voltage  $V_R$ .

In this clipper circuit,

If  $v_i > V_R$ , diode is reverse biased.  $v_o = v_i$

and, If  $v_i < V_R$ , diode is forward biased.  $v_o = V_R$

The transfer characteristic of the circuit is shown in **fig. 6**.

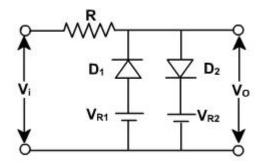

Clipper Circuit 3: To clip the input signal between two independent levels ( $V_{R1} < V_{R2}$ ), the clipper circuit is shown in <u>fig. 7</u>.

The diodes  $D_1 \& D_2$  are assumed ideal diodes.

For this clipper circuit, when  $v_i \leq V_{R1}, \, v_o \!\!=\!\! V_{R1}$

and,  $v_i \ge V_{R2}$ ,  $v_o = V_{R2}$

and,  $V_{R1} < v_i < V_{R2} \ v_o = v_i$

The transfer characteristic of the clipper is shown in fig. 8.

#### **Clippers:**

Clipping circuits are used to select that portion of the input wave which lies above or below some reference level. Some of the clipper circuits are discussed here. The transfer characteristic (v<sub>o</sub> vs v<sub>i</sub>) and the output voltage waveform for a given input voltage are also discussed.

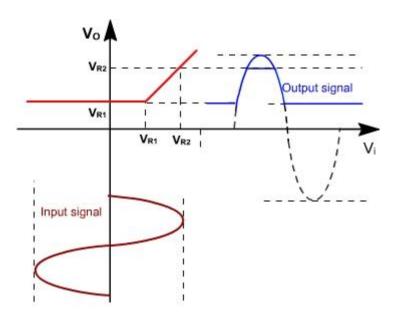

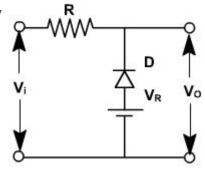

#### **Clipper Circuit 1:**

The circuit shown in <u>fig. 3</u>, clips the input signal above a reference voltage  $(V_R)$ .

In this clipper circuit,

If  $v_i < V_{\text{R}},$  diode is reversed biased and does not conduct. Therefore,  $v_{\text{o}} = v_i$

and, if  $v_i > V_R$ , diode is forward biased and thus,  $v_0 = V_R$ .

The transfer characteristic of the clippers is shown in <u>fig. 4</u>.

Fig. 3

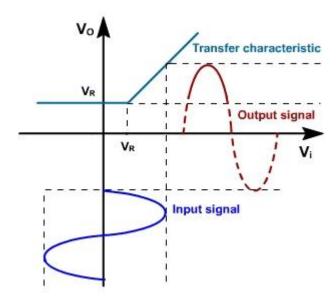

### **Clipper Circuit 2:**

The clipper circuit shown in <u>fig. 5</u> clips the input signal below reference voltage  $V_R$ .

In this clipper circuit,

If  $v_i > V_R$ , diode is reverse biased.  $v_o = v_i$

and, If  $v_i < V_R$ , diode is forward biased.  $v_o = V_R$

The transfer characteristic of the circuit is shown in **<u>fig. 6</u>**.

15EE34

Fig. 6

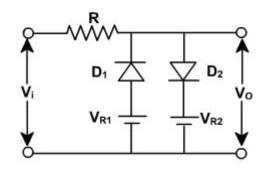

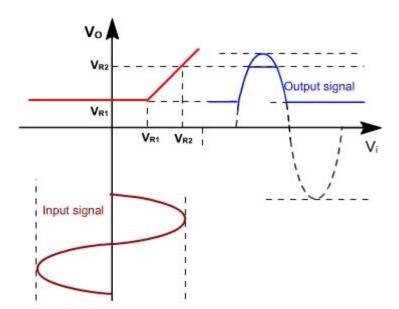

### **Clipper Circuit 3:**

To clip the input signal between two independent levels  $(V_{R1} < V_{R2})$ , the clipper circuit is shown in <u>fig. 7</u>.

The diodes  $D_1 \& D_2$  are assumed ideal diodes.

For this clipper circuit, when  $v_i \leq V_{R1}, \, v_o \!\!=\!\! V_{R1}$

and,  $v_i \geq V_{R2}, \, v_o \!\!= V_{R2}$

and,  $V_{R1} < v_i < V_{R2}$   $v_o = v_i$

The transfer characteristic of the clipper is shown in <u>fig. 8</u>.

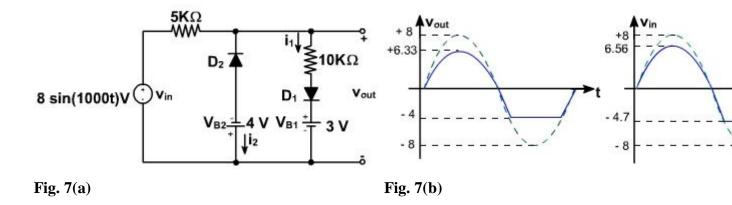

### Example - 1:

Find the output voltage v out of the clipper circuit of fig. 7(a) assuming that the diodes are

- a. ideal.

- b.  $V_{on} = 0.7$  V. For both cases, assume  $R_F$  is zero.

#### Solution:

(a). When  $v_{in}$  is positive and  $v_{in} < 3$ , then  $v_{out} = v_{in}$

and when  $v_{in}$  is positive and  $v_{in} > 3$ , then

$$i_{1} = \frac{v_{in} - 3}{1.5 \times 10^{4}}$$

$$v_{out} = 10^{4}i_{1} + 3 = \frac{2}{3}v_{in} + 1$$

At

$$v_{in} = 8 V(peak)$$

,  $v_{out} = 6.33 V$ .

When  $v_{in} is$  negative and  $v_{in} >$  - 4, then  $v_{out} = v_{in}$

When  $v_{in}$  is negative and  $v_{in} < -4$ , then  $v_{out} = -4V$

The resulting output wave shape is shown in **fig. 7(b)**.

(b). When  $V_{ON} = 0.7$  V,  $v_{in}$  is positive and  $v_{in} < 3.7$  V, then  $v_{out} = v_{in}$

When  $v_{in} > 3.7$  V, then

$$i_1 = \frac{v_{in} - 3.7}{1.5 \times 10^4}$$

$$v_{out} = 10^4 i_1 + 3.7 = \frac{2}{3} v_{in} + 1.23$$

When  $v_{in} = 8V$ ,  $v_{out} = 6.56$  V.

When  $v_{in}$  is negative and  $v_{in} > -4.7$  V, then  $v_{out} = v_{in}$

When  $v_{in} < -4.7$  V, then  $v_{out} = -4.7$  V

The resulting output wave form is shown in **fig. 7(b)**.

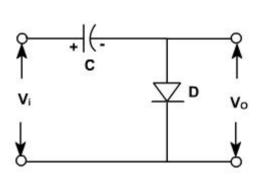

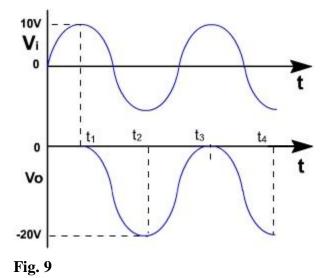

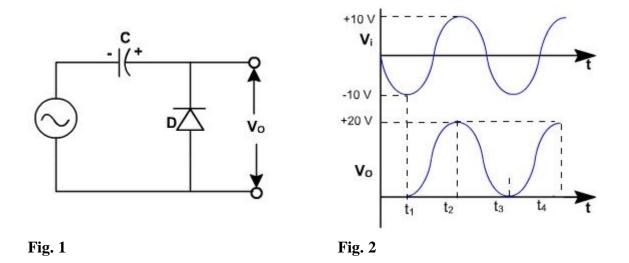

### **Clamper Circuits:**

Clamping is a process of introducing a dc level into a signal. For example, if the input voltage swings from -10 V and +10 V, a positive dc clamper, which introduces +10 V in the input will produce the output that swings ideally from 0 V to +20 V. The complete waveform is lifted up by +10 V.

### Negative Diode clamper:

A negative diode clamper is shown in <u>fig. 8</u>, which introduces a negative dc voltage equal to peak value of input in the input signal.

### Fig. 8

- Let the input signal swings form +10 V to -10 V. During first positive half cycle as V i rises from 0 to 10 V, the diode conducts. Assuming an ideal diode, its voltage, which is also the output must be zero during the time from 0 to t<sub>1</sub>. The capacitor charges during this period to 10 V, with the polarity shown.

- At that  $V_i$  starts to drop which means the anode of D is negative relative to cathode, ( $V_D = v_i - v_c$ ) thus reverse biasing the diode and preventing the capacitor from discharging. <u>Fig. 9</u>. Since the capacitor is holding its charge it behaves as a DC voltage source while the diode appears as an open circuit, therefore the equivalent circuit

Analog electronic Circuits

becomes an input supply in series with -10 V dc voltage as shown in <u>fig. 10</u>, and the resultant output voltage is the sum of instantaneous input voltage and dc voltage (-10 V).

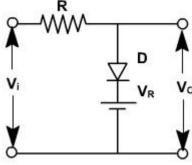

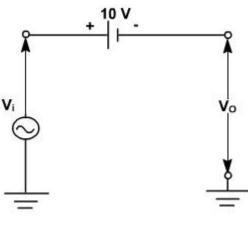

#### **Positive Clamper:**

The positive clamper circuit is shown in <u>fig. 1</u>, which introduces positive dc voltage equal to the peak of input signal. The operation of the circuit is same as of negative clamper.

- Let the input signal swings form +10 V to -10 V. During first negative half cycle as  $V_i$  rises from 0 to -10 V, the diode conducts. Assuming an ideal diode, its voltage, which is also the output must be zero during the time from 0 to  $t_1$ . The capacitor charges during this period to 10 V, with the polarity shown.

- After that  $V_i$  starts to drop which means the anode of D is negative relative to cathode, ( $V_D = v_i v_C$ ) thus reverse biasing the diode and preventing the capacitor from discharging. <u>Fig. 2</u>. Since the capacitor is holding its charge it behaves as a DC voltage source while the diode appears as an open circuit, therefore the equivalent circuit becomes an input supply in series with +10 V dc voltage and the resultant output voltage is the sum of instantaneous input voltage and dc voltage (+10 V).

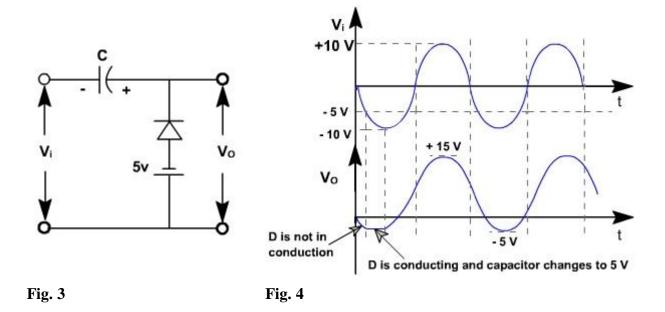

- To clamp the input signal by a voltage other than peak value, a dc source is required. As shown in **fig. 3**, the dc source is reverse biasing the diode.

- The input voltage swings from +10 V to -10 V. In the negative half cycle when the voltage exceed 5V then D conduct. During input voltage variation from ?5 V to -10 V, the capacitor charges to

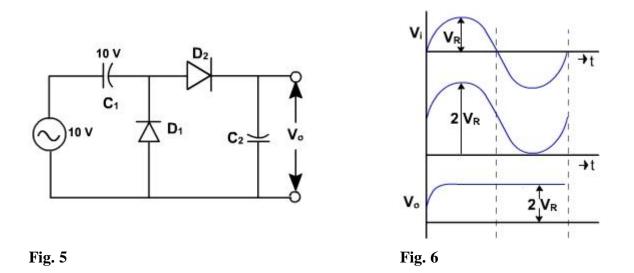

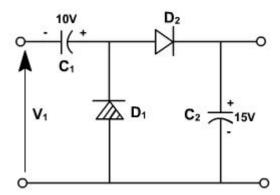

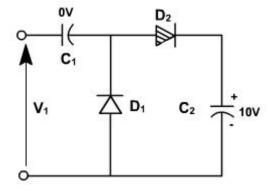

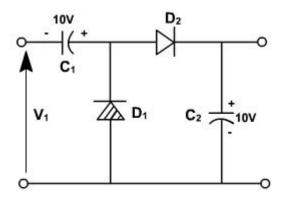

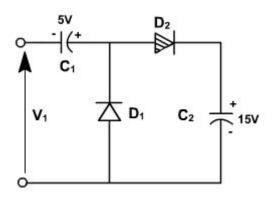

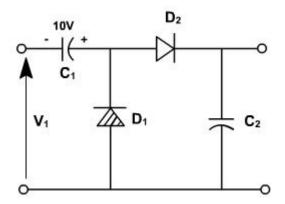

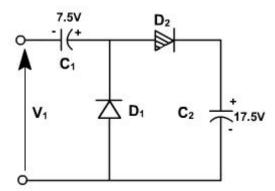

### **Voltage Doubler :**

A voltage doubler circuit is shown in <u>fig. 5</u>. The circuit produces a dc voltage, which is double the peak input voltage.

At the peak of the negative half cycle  $D_1$  is forward based, and  $D_2$  is reverse based. This charges  $C_1$  to the peak voltage  $V_p$  with the polarity shown. At the peak of the positive half cycle  $D_1$  is reverse biased and  $D_2$  is forward biased. Because the source and  $C_1$  are in series,  $C_2$  will change toward  $2V_p$ . e.g. Capacitor voltage increases continuously and finally becomes 20V. The voltage waveform is shown in <u>fig. 6</u>.

15EE34

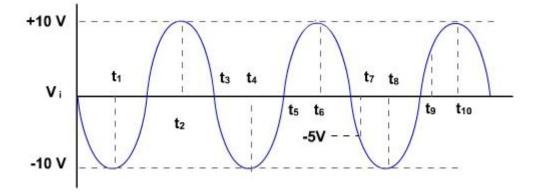

To understand the circuit operation, let the input voltage varies from -10 V to +10 V. The different stages of circuit from 0 to  $t_{10}$  are shown in <u>fig. 7(a)</u>.

During 0 to  $t_1$ , the input voltage is negative,  $D_1$  is forward biased the capacitor is charged to ?10 V with the polarity as shown in <u>fig. 7b</u>.

#### **Fig. 7(b)**

During  $t_1$  to  $t_2$ ,  $D_2$  becomes forward biased and conducts and at  $t_2$ , when  $V_i$  is 10V total voltage change is 20V. If  $C_1 = C_2 = C$ , both the capacitor voltages charge to +10 V i.e.  $C_1$  voltage becomes 0 and  $C_2$  charges to +10V.

From  $t_2$  to  $t_3$  there is no conduction as both  $D_1$  and  $D_2$  are reverse biased. During  $t_3$  to  $t_4$   $D_1$  is forward biased and conducts.  $C_1$  again charges to +10V

During  $t_4$  to  $t_5$  both  $D_1$  and  $D_2$  are reverse biased and do not conduct. During  $t_5$  to  $t_6 D_2$  is forward biased and conducts. The capacitor  $C_2$  voltage becomes +15 V and  $C_1$  voltage becomes +5 V.

Fig. 7(e)

Again during  $t_6$  to  $t_7$  there is no conduction and during  $t_7$  to  $t_8$ ,  $D_1$  conducts. The capacitor  $C_1$  recharges to 10 V.

During  $t_8$  to  $t_9$  both  $D_1$  and  $D_2$  are reverse biased and there is no conduction. During  $t_9$  to  $t_{10}$   $D_2$  conducts and capacitor  $C_2$  voltage becomes + 17.5 V and  $C_1$  voltage becomes 7.5V. This process continues till the capacitor  $C_1$  voltage becomes +20V.

The power handling capacity of these diodes is better. The power dissipation of a zener diode equals the product of its voltage and current.

#### $P_Z = V_Z I_Z$

The amount of power which the zener diode can withstand (  $V_Z.I_{Z(max)}$  ) is a limiting factor in power supply design.

# **Transistor biasing**

To Understand :

- Concept of Operating point and stability

- Analyzing Various biasing circuits and their comparison with respect to stability

### **BJT – A Review**

- Invented in 1948 by Bardeen, Brattain and Shockley

- Contains three adjoining, alternately doped semiconductor regions: Emitter (E), Base (B), and Collector (C)

- The middle region, base, is very thin

- Emitter is heavily doped compared to collector. So, emitter and collector are not interchangeable.

### Three operating regions

- Linear region operation:

- Base emitter junction forward biased

- Base collector junction reverse biased

- **Cutoff region** operation:

- Base emitter junction reverse biased

- Base collector junction reverse biased

- **Saturation region** operation:

- Base emitter junction forward biased

- Base collector junction forward biased

#### Three operating regions of BJT

- Cut off:  $V_{CE} = V_{CC}$ ,  $I_C \cong 0$

- Active or linear : VCE  $\cong$  VCC/2 , IC  $\cong$  IC max/2

- Saturation: VCE  $\cong 0$ , IC  $\cong$  IC max

### **Q-Point**

- The intersection of the dc bias value of *IB* with the dc load line determines the *Q* point.

- It is desirable to have the *Q*-point centered on the load line. Why?

- When a circuit is designed to have a centered *Q*-point, the amplifier is said to be midpoint biased.

- Midpoint biasing allows optimum ac operation of the amplifier.

#### **Introduction - Biasing**

- The analysis or design of a transistor amplifier requires knowledge of both the dc and ac response of the system. In fact, the amplifier increases the strength of a weak signal by transferring the energy from the applied DC source to the weak input ac signal

- The analysis or design of any electronic amplifier therefore has two components:

- The dc portion and

- The ac portion

During the design stage, the choice of parameters for the required dc levels will affect the ac response.

#### What is biasing circuit?

Once the desired dc current and voltage levels have been identified, a network must be constructed that will establish the desired values of IB, IC and VCE, Such a network is known as biasing circuit. A biasing network has to preferably make

use of one power supply to bias both the junctions of the transistor.

#### Purpose of the DC biasing circuit

- To turn the device "ON"

- To place it in operation in the region of its characteristic where the device operates most linearly, i.e. to set up the initial dc values of *IB*, *IC*, and *VCE*

#### Important basic relationship

- $V_{BE} = 0.7V$

- $IE = (\beta + 1) IB \cong IC$

- IC =  $\beta$  IB

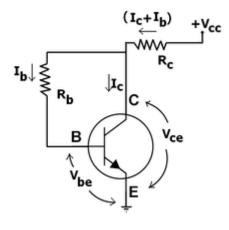

**Collector-to-base bias**

5

Collector-to-base bias

This configuration employs <u>negative feedback</u> to prevent <u>thermal runaway</u> and stabilize the operating point. In this form of biasing, the base resistor  $R_B$  is connected to the collector instead of connecting it to the DC source  $V_{CC}$ . So any thermal runaway will induce a voltage drop across the  $R_C$  resistor that will throttle the transistor's base current.

From <u>Kirchhoff's voltage law</u>, the voltage  $V_{\mathbf{R}_{b}}$  across the base resistor  $R_{b}$  is

$$V_{\rm R_b} = V_{\rm cc} - \underbrace{\overbrace{(I_{\rm c} + I_{\rm b})R_{\rm c}}^{\rm Voltage drop across R_c}}_{\rm V_{\rm R_b}} - \underbrace{V_{\rm obtage at base}}_{V_{\rm be}}$$

By the <u>Ebers–Moll model</u>,  $I_c = \beta I_b$ , and so

$$V_{\rm R_b} = V_{\rm cc} - (\beta I_{\rm b} + I_{\rm b})R_{\rm c} - V_{\rm be} = V_{\rm cc} - I_{\rm b}(\beta + 1)R_{\rm c} - V_{\rm be}.$$

From Ohm's law, the base current  $I_{\rm b} = V_{\rm R_b}/R_{\rm b, and so}$

$$\overbrace{I_{\rm b}R_{\rm b}}^{V_{\rm R_{\rm b}}} = V_{\rm cc} - I_{\rm b}(\beta + 1)R_{\rm c} - V_{\rm be}$$

Hence, the base current  $I_{\rm b}$  is

$$I_{\rm b} = \frac{V_{\rm cc} - V_{\rm be}}{R_{\rm b} + (\beta + 1)R_{\rm c}}$$

If  $V_{\rm be}$  is held constant and temperature increases, then the

collector current  $I_c$  increases. However, a larger  $I_c$  causes the voltage drop across resistor  $R_c$  to increase, which in turn reduces the voltage  $V_{R_b}$  across the base resistor  $R_b$ . A lower base-resistor voltage drop reduces the base current  $I_b$ , which results in less collector current  $I_c$ . Because an increase in collector current with temperature is opposed, the operating point is kept stable.

#### Merits:

• Circuit stabilizes the operating point against variations in temperature and  $\beta$  (ie. replacement of transistor)

#### **Demerits:**

• In this circuit, to keep  $I_c$  independent of  $\beta$ , the following condition must be met:

$$I_{\rm c} = \beta I_{\rm b} = \frac{\beta (V_{\rm cc} - V_{\rm be})}{R_{\rm b} + R_{\rm c} + \beta R_{\rm c}} \approx \frac{(V_{\rm cc} - V_{\rm be})}{R_{\rm c}}$$

which is the case when

$$\beta R_{\rm c} \gg R_{\rm b}$$

- As  $\beta$ -value is fixed (and generally unknown) for a given transistor, this relation can be satisfied either by keeping  $R_c$  fairly large or making  $R_b$  very low.

- If  $R_c$  is large, a high  $V_{cc}$  is necessary, which increases cost as well as precautions necessary while handling.

- If  $R_b$  is low, the reverse bias of the collector-base region is small, which limits the range of collector voltage swing that leaves the transistor in active mode.

- The resistor  $R_b$  causes an <u>AC</u> feedback, reducing the <u>voltage gain</u> of the amplifier. This undesirable effect is a trade-off for greater <u>Q-point</u> stability.

**Usage:** The feedback also decreases the input impedance of the amplifier as seen from the base, which can be advantageous. Due to the gain reduction from feedback, this biasing form is used only when the trade-off for stability is warranted

15EE34

# **Biasing circuits:**

- Fixed bias circuit

- Emitter bias

- Voltage divider bias

- DC bias with voltage feedback

- Miscellaneous bias

- The simplest transistor dc bias configuration.

- For dc analysis, open all the capacitance.

## **DC** Analysis

• Applying KVL to the input loop:

VCC = IBRB + VBE

• From the above equation, deriving for IB, we get,

IB = [VCC - VBE] / RB

- The selection of  $R_B$  sets the level of base current for the operating point.

- Applying KVL for the output loop:

VCC = ICRC + VCE

S(ICO) =  $\beta$  + 1

This indicates poor stability.

## Voltage divider configuration

S(ICO) =  $(\beta + 1) [1 + RB / RE] / [(\beta + 1) + RB / RE]$  Here, replace RB with Rth

S(ICO) =  $(\beta + 1) [1 + R_{th} / R_{E}] / [(\beta + 1) + R_{th} / R_{E}]$

Thus, voltage divider bias configuration is quite stable when the ratio R / R  $\,$  is as small

### **Physical impact**

In a **fixed bias circuit**, IC increases due to increase in IC0. [IC =  $\beta$ IB + ( $\beta$ +1) IC0]

IB is fixed by VCC and RB. Thus level of IC would continue to rise with temperature -

a very unstable situation.

- In emitter bias circuit, as I<sub>C</sub> increases, I<sub>E</sub> increases, V<sub>E</sub> increases. Increase in V<sub>E</sub> reduces I<sub>B</sub>. I<sub>B</sub> =  $[V_{CC} V_{BE} V_{E}] / R_{B}$ . A drop in I<sub>B</sub> reduces I<sub>C</sub>. Thus, this configuration is such that there is a reaction to an increase in I<sub>C</sub> that will tend to oppose the change in bias conditions.

- In the **DC bias with voltage feedback**, as I<sub>C</sub> increases, voltage across R<sub>C</sub> increases, thus reducing I<sub>B</sub> and causing I<sub>C</sub> to reduce.

The most stable configuration is the voltage – divider network. If the condition  $\beta R_E$

$>>10R_2$ , the voltage VB will remain fairly constant for changing levels of IC. VBE =

VB – VE, as IC increases, VE increases, since VB is constant, VBE drops making IB to

fall, which will try to offset the increases level of IC.

# S(VBE)

$S(V_{BE}) = \Delta I_C / \Delta V_{BE}$

For an emitter bias circuit,  $S(VBE) = -\beta / [RB + (\beta + 1)RE]$

If RE =0 in the above equation, we get S(VBE) for a fixed bias circuit as, S(VBE) = -  $\beta$ /RB.

## For an emitter bias,

$S(VBE) = -\beta / [RB + (\beta + 1)RE] \text{ can be}$ rewritten as,  $S(VBE) = -(\beta/RE) / [RB/RE + (\beta + 1)]$

If  $(\beta + 1) >> RB/RE$ , then

The larger the  $R_E$ , lower the  $S(V_{BE})$  and more stable is the system. Total effect of all the three parameters on  $I_C$  can be written as,

Forward active mode of operation

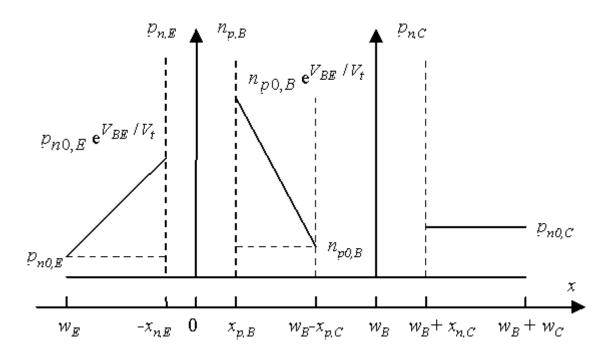

The forward active mode is obtained by forward-biasing the base-emitter junction. In addition we eliminate the base-collector junction current by setting  $V_{BC} = 0$ . The minority-carrier distribution in the quasi-neutral regions of the bipolar transistor, as shown in Figure, is used to analyze this situation in more detail.

Minority-carrier distribution in the quasi-neutral regions of a bipolar transistor (a) Forward active bias mode. (b) Saturation mode.

The values of the minority carrier densities at the edges of the depletion regions are indicated on the Figure. The carrier densities vary linearly between the boundary values as expected when using the assumption that no significant recombination takes place in the quasi-neutral regions. The minority carrier densities on both sides of the base-collector depletion region equal the thermal equilibrium values since  $V_{BC}$  was set to zero. While this boundary condition is mathematically equivalent to that of an ideal contact, there is an important difference. The minority carriers arriving at  $x = w_B - x_{p,BC}$  do not recombine. Instead, they drift through the base-collector depletion region and end up as majority carriers in the collector region.

$$I_{E,n} = qn_i^2 A_E \left(\frac{D_{n,B}}{N_B w_B^{'}}\right) \left(\exp(\frac{V_{BE}}{V_t}) - 1\right)$$

$$I_{E,p} = qn_i^2 A_E \left(\frac{D_{p,E}}{N_E w_E^{'}}\right) \left(\exp(\frac{V_{BE}}{V_t}) - 1\right)$$

$$\Delta Q_{n,B} = qA_E \int_{x_{p,E}}^{w_B - x_{p,C}} n_p(x) - n_{p0} dx$$

$$\Delta Q_{n,B} = qA_E \frac{n_i^2}{N_B} \left( \exp(\frac{V_{BE}}{V_t}) - 1 \right) \frac{w_B'}{2}$$

And the emitter current due to electrons,  $I_{E,n}$ , simplifies to:

$$I_{E,n} = \frac{\Delta Q_{n,B}}{t_r}$$

It is convenient to rewrite the emitter current due to electrons,  $I_{E,n}$ , as a function of the total excess minority charge in the base,  $\Box Q_{n,B}$ . This charge is proportional to the triangular area in the quasi-neutral base as shown in Figure and is calculated from

where  $t_r$  is the average time the minority carriers spend in the base layer, i.e. the transit time. The emitter current therefore equals the excess minority carrier charge present in the base region, divided by the time this charge spends in the base. This and other similar relations will be used to construct the charge control model of the bipolar junction transistor A combination of equations yields the transit time as a function of the quasi-neutral layer width,  $w_B$ , and the electron diffusion constant in the base,  $D_{n,B}$ .

$$t_r = \frac{w_B^{\prime 2}}{2D_{n,B}}$$

We now turn our attention to the recombination current in the quasi-neutral base and obtain it

from the continuity equation

$$\frac{\partial n_p(x)}{\partial t} = \frac{1}{q} \frac{\partial J_n(x)}{\partial x} - \frac{n_p(x) - n_{p0}}{\tau_n} - \frac{\eta_p(x) - \eta_{p0}}{\tau_n} - \frac{\eta_p(x) - \eta_p(x) - \eta_p(x)$$

By applying it to the quasi-neutral base region and assuming steady state conditions:

$$I_{r,B} = qA_E \int_{x_{p,BE}}^{w_B - x_{p,BC}} \frac{n_p(x) - n_{p0}}{\tau_n} dx$$

which in turn can be written as a function of the excess minority carrier charge,  $\Box Q_{n,B}$ , using

$$I_{r,B} = \frac{\Delta Q_{n,B}}{\tau_n}$$

equation

$$\gamma_E = \frac{1}{1 + \frac{D_{p,E}N_Bw_B'}{D_{n,B}N_Ew_E'}}$$

It is typically the emitter efficiency, which limits the current gain in transistors made of silicon or germanium. The long minority-carrier lifetime and the long diffusion lengths in those materials justify the exclusion of recombination in the base or the depletion layer. The resulting current gain, under such conditions, is:

$$\boldsymbol{\beta} \cong \frac{D_{n,B} N_E \boldsymbol{w}_E'}{D_{p,E} N_B \boldsymbol{w}_B'}, \quad \text{if} \quad \boldsymbol{\alpha} \cong \boldsymbol{\gamma}_E$$

From this equation, we conclude that the current gain can be larger than one if the emitter doping is much larger than the base doping. A typical current gain for a silicon bipolar transistor is 50 - 150.

$$\alpha_T = 1 - \frac{t_r}{\tau_n} = 1 - \frac{w_B^2}{2D_{n,B}\tau_n}$$

This expression is only valid if the base transport factor is very close to one, since it was derived using the "short-diode" carrier distribution. This base transport factor can also be

$$\alpha_T = 1 - \frac{1}{2} (\frac{w_B'}{L_n})^2$$

expressed in function of the diffusion length in the base:

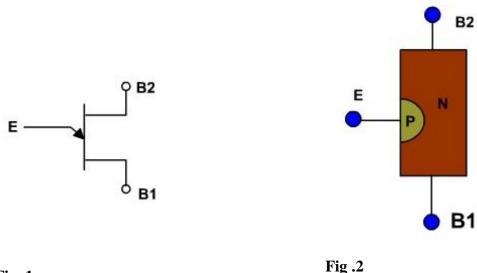

#### **Uni-junction transistor**

- The UJT as the name implies, is characterized by a single pn junction. It exhibits negative resistance characteristic that makes it useful in oscillator circuits.

- The symbol for UJT is shown in <u>fig. 1</u>. The UJT is having three terminals base1 (B1), base2 (B2) and emitter (E). The UJT is made up of an N-type silicon bar which acts as the base as shown in <u>fig. 2</u>. It is very lightly doped. A P-type impurity is introduced into the base, producing a single PN junction called emitter. The PN junction exhibits the properties of a conventional diode.

## Fig. 1

- A complementary UJT is formed by a P-type base and N-type emitter. Except for the polarity of voltage and current the characteristic is similar to those of a conventional UJT.

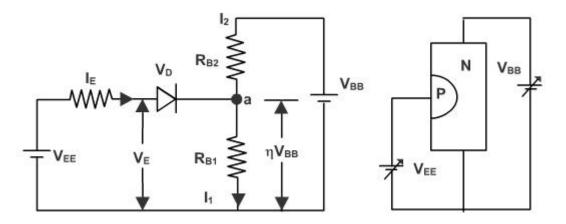

- A simplified equivalent circuit for the UJT is shown in <u>fig. 3</u>. V<sub>BB</sub> is a source of biasing voltage connected between B2 and B1. When the emitter is open, the total resistance from B2 to B1 is simply the resistance of the silicon bar, this is known as the inter base resistance R<sub>BB</sub>. Since the N-channel is lightly doped, therefore R<sub>BB</sub> is relatively high, typically 5 to 10K ohm. R<sub>B2</sub> is the resistance between B2 and point ?a', while R<sub>B1</sub> is the resistance from point ?a' to B1, therefore the interbase resistance R<sub>BB</sub> is

$R_{BB}=R_{B1}+R_{B2}$

#### Fig. 3

- The diode accounts for the rectifying properties of the PN junction.  $V_D$  is the diode's threshold voltage. With the emitter open,  $I_E = 0$ , and  $I_1 = I_2$ . The interbase current is given by

- $I_1 = I_2 = V_{BB} \ / \ R \ _{BB}$  .

- Part of  $V_{BB}$  is dropped across  $R_{B2}$  while the rest of voltage is dropped across  $R_{B1}$ . The voltage across  $R_{B1}$  is

$$V_a = V_{BB} * (R_{B1}) / (R_{B1} + R_{B2})$$

The ratio  $R_{B1}$  / ( $R_{B1}$  +  $R_{B2}$ ) is called intrinsic standoff ratio

- $\Box = R_{B1} / (R_{B1} + R_{B2})$  i.e.  $V_a = \Box V_{BB}$ .

- The ratio  $\Box$  is a property of UJT and it is always less than one and usually between 0.4 and 0.85. As long as  $I_B = 0$ , the circuit of behaves as a voltage divider.

- Assume now that  $v_E$  is gradually increased from zero using an emitter supply  $V_{EE}$ . The diode remains reverse biased till  $v_E$  voltage is less than  $\Box V_{BB}$  and no emitter current flows except leakage current. The emitter diode will be reversed biased.

- When  $v_E = V_D + \Box V_{BB}$ , then appreciable emitter current begins to flow where  $V_D$  is the diode's threshold voltage. The value of  $v_E$  that causes, the diode to start conducting is called the peak point voltage and the current is called peak point current  $I_P$ .

$V_P = V_D + \Box \ V_{BB}.$

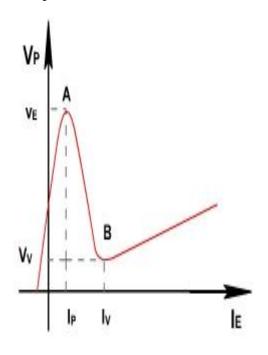

- The graph of <u>fig. 4</u> shows the relationship between the emitter voltage and current.  $v_E$  is plotted on the vertical axis and  $I_E$  is plotted on the horizontal axis. The region from  $v_E = 0$  to  $v_E = V_P$  is called cut off region because no emitter current flows (except for leakage). Once  $v_E$ exceeds the peak point voltage,  $I_E$  increases, but  $v_E$  decreases. up to certain point called valley point ( $V_V$  and  $I_V$ ). This is called negative resistance region. Beyond this,  $I_E$  increases with  $v_E$  this is the saturation region, which exhibits a positive resistance characteristic.

- The physical process responsible for the negative resistance characteristic is called conductivity modulation. When the  $v_E$  exceeds  $V_P$  voltage, holes from P emitter are injected into N base. Since the P region is heavily doped compared with the N-region, holes are injected to the lower half of the UJT

The lightly doped N region gives these holes a long lifetime. These holes move towards B1 to complete their path by re-entering at the negative terminal of  $V_{EE}$ . The large holes create a conducting path between the emitter and the lower base. These increased charge carriers

represent a decrease in resistance  $R_{B1}$ , therefore can be considered as variable resistance. It decreases up to 50 ohm.

- Since  $\Box$  is a function of  $R_{B1}$  it follows that the reduction of  $R_{B1}$  causes a corresponding reduction in intrinsic standoff ratio. Thus as  $I_E$  increases,  $R_{B1}$  decreases,  $\Box$  decreases, and  $V_a$  decreases. The decrease in V  $_a$  causes more emitter current to flow which causes further reduction in  $R_{B1}$ ,  $\Box$ , and  $V_a$ . This process is regenerative and therefore  $V_a$  as well as  $v_E$  quickly drops while  $I_E$  increases. Although  $R_B$  decreases in value, but it is always positive resistance. It is only the dynamic resistance between  $V_V$  and  $V_P$ . At point B, the entire base1 region will saturate with carriers and resistance  $R_{B1}$  will not decrease any more. A further increase in  $I_e$  will be followed by a voltage rise.

- The diode threshold voltage decreases with temperature and  $R_{BB}$  resistance increases with temperature because Si has positive temperature coefficient.

### **UJT Relaxation Oscillator:**

- The characteristic of UJT was discussed in previous lecture. It is having negative resistance region. The negative dynamic resistance region of UJT can be used to realize an oscillator.

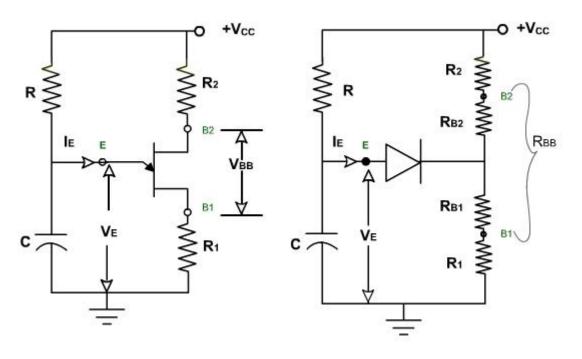

- The circuit of UJT relaxation oscillator is shown in <u>fig. 1</u>. It includes two resistors  $R_1$  and  $R_2$  for taking two outputs  $R_2$  may be a few hundred ohms and  $R_1$  should be less than 50 ohms. The dc source  $V_{CC}$  supplies the necessary bias. The interbase voltage  $V_{BB}$  is the difference between  $V_{CC}$  and the voltage drops across  $R_1$  and  $R_2$ . Usually  $R_{BB}$  is much larger than  $R_1$  and  $R_2$  so that  $V_{BB}$  approximately equal to V. Note,  $R_{B1}$  and  $R_{B2}$  are inter-resistance of UJT while  $R_1$  and  $R_2$  is the actual resistor.  $R_{B1}$  is in series with  $R_1$  and  $R_{B2}$  is in series with  $R_2$ .

Fig. 1

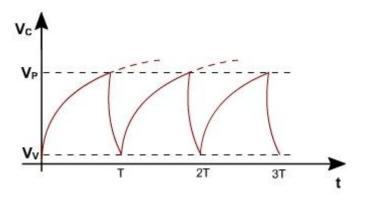

As soon as power is applied to the circuit capacitor begins to charge toward V. The voltage across C, which is also  $V_E$ , rises exponentially with a time constant

$\Box = R C$

- As long as  $V_E < V_P$ ,  $I_E = 0$ . the diode remains reverse biased as long as  $V_E < V_P$ . When the capacitor charges up to  $V_P$ , the diode conducts and  $R_{B1}$  decreases and capacitor starts discharging. The reduction in R <sub>B1</sub> causes capacitor C voltage to drop very quickly to the valley voltage  $V_V$  because of the fast time constant due to the low value of  $R_{B1}$  and  $R_1$ . As soon as  $V_E$  drops below  $V_a + V_D$  the diode is no longer forward biased and it stops conduction. It now reverts to the previous state and C begins to charge once more toward  $V_{CC}$ .

- The emitter voltage is shown in <u>fig. 2</u>,  $V_E$  rises exponentially toward  $V_{CC}$  but drops to a very low value after it reaches  $V_P$ . The time for the  $V_E$  to drop from  $V_P$  to  $V_V$  is relatively small and usually neglected. The period T can therefore be approximated as follows:

# **Fig. 2**

Let T be the Time required for  $V_{\mathsf{E}}$  to rise from 0 to  $V_{\mathsf{P}}.$

$As \log as R_{BB} >> (R_1 + R_2);$

$\lor_{BB} \approx \lor_{CC}$  and  $\lor_{P}$  =  $\eta \lor_{CC}$

The capacitor charging voltage is given by

$$V_{\rm E} = V_{\rm CC} (1 - e^{-\frac{1}{2} \frac{1}{RC}})$$

Where  $V_{\mathsf{E}}$  is the instantaneous capacitor voltage.

Note that at

$$t = T$$

,  $\forall_E = \forall_P = \eta \forall_{CC}$

$\eta \forall = \forall_{CC} (1 - e^{-T_{RC}})$

$or \qquad \eta \!=\! (1\!-\!e^{-T_{\rm RC}})$

Thus

$$e^{T/Rc} = \frac{1}{1-\eta}$$

$$T = RC \ln \left(\frac{1}{1-\eta}\right)$$

$$T = RC K$$

The frequency of oscillation is, therefore, given by

$$f_c = \frac{1}{T} \frac{1}{RCK}$$

The parameter Kvaries with η

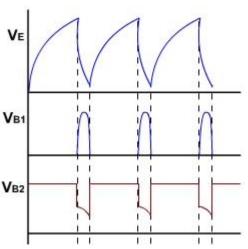

- There are two additional outputs possible for the UJT oscillation one of these is the voltage developed at B1 due to capacitor discharge while the other is voltage developed at B2 as shown in **fig. 3**.

- When UJT fires (at t = T) V<sub>a</sub> drops, causing a corresponding voltage drop at B2. The duration of outputs at B1 and B2 are determined by C discharge time.

- If  $R_1$  is very small, C discharges very quickly and very narrow pulse is produced at the output. If  $R_1 = 0$ , obviously no pulses appear at B1.

- If  $R_2 = 0$ , no pulse can be generated at B2. If  $R_1$  is too large, its positive resistance may swamp the negative resistance and prevent the UJT form switching back after it has fired.

- $R_2$ , in addition to providing a source of pulse at B2, is useful for temperature stabilization of the UJT's peak VB2 point voltage .

$V_P = V_D + \Box \ V_{BB}.$

As the temperature increases,  $V_p$  decreases. The temperature coefficient of  $R_{BB}$  is positive.  $R_s$  is essentially independent of temperature. It is therefore possible to select  $R_2$  so that  $\Box$   $V_{BB}$  increases with temperature by the same amount as  $V_D$  decreases. This provides a constant  $V_P$  and, in turn, frequency of oscillation.

#### Selection of R and C:

In the circuit, R is required to pass only the capacitor charging current. At the instant when  $V_P$  is reached; R must supply the peak current. It is therefore, necessary, that the current through R should be slightly greater than the peak point.

$$|_{R} > |_{P}$$

$$\frac{\bigvee_{CC} - \bigvee_{P}}{R} > |_{P}$$

$$R < \frac{\bigvee_{CC} - \bigvee_{P}}{|_{P}}$$

Once the UJT fires,  $V_E$  drops to the valley voltage  $V_V$ .  $I_E$  should not be allowed to increases beyond the valley point  $I_V$ , otherwise the UJT is taken into saturation region and does not switch back, R therefore must be selected large enough to ensure that

$$|_{E} < I_{\vee}$$

$$\frac{V_{cc} - V_{\vee}}{R} < I_{\vee}$$

$$R > \frac{V_{cc} - V_{\vee}}{I_{\vee}}$$

Therefore,

$$\frac{V_{cc} - V_{\vee}}{I_{P}} > R > \frac{V_{cc} - V_{\vee}}{I_{\vee}}$$

As long as R is chosen between these extremes, reliable operation results.